ECE 383 - Embedded

Computer Systems II

Lecture 2 - Digital

System, Hierarchical

Design, and testbench

> Sandbox\_tb.vhdl

#### HW#1 VHDL Code

Is this Behavioral or Structural code?

#### **Lesson Outline**

- 1. Overview of HDLs

- 2. Basic VHDL concepts by example

- 3. Testbenches

### **Overview of HDLs**

## **Programming Language**

Python?

■ Can we use C or Java as an HDL?

need

-

#### **HDL vs Traditional PL**

- Traditional PL

- Modeled after a sequential process

- Operations performed in a sequential order

- Help human's thinking process to develop an algorithm step-by-step

- Resemble the operation of a basic computer model

- HDL

- Characteristics of digital hardware

- Connections of parts

- Concurrent operations

- Concept of propagation delay and timing

- Characteristics cannot be captured by traditional PLs

- Require new languages: HDL

#### **Modern Use of HDLs**

- Formal Documentation

- Input to a simulator

- Input to a synthesizer <

### **Characteristics of an HDL**

- Capture characteristics of a digital circuit:

- BBB Part Entity - basic building block (e.g. 7400 chips)

- Connectivity Connection of entities (e.g. wires)

- **Concurrency parallel operations**

- Timing schedule / order of multiple operations

- Must be able to describe a circuit in

- Gate level and RT level

- Structural view and behavioral view (not physical)

## **Industry-Standard HDLs**

- VHDL ~ Or Yx K

- DoD initiative in 1980s

- Transferred to IEEE to standardize

- First released in 1987

- Similar to Ada

- Heavily used in FPGA industry

- New versions: 1993, 2001, 2008

- Verilog ← Back

- Developed by industry

- Released in early 1980s

- Similar to 🕏

- Heavily used in ASIC industry

- New versions: 1995, 2001, 2005

- SystemVerilog is a superset of Verilog 2005

# **Basic VHDL Concepts By Example**

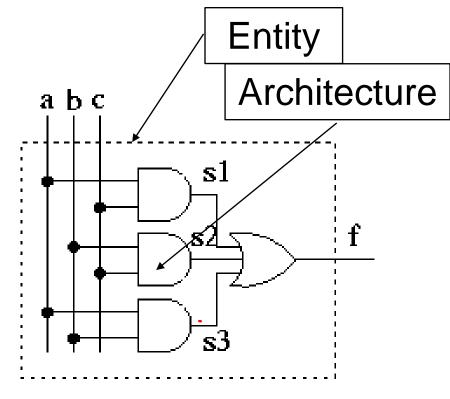

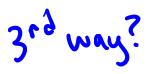

## **Structural Description**

#### Structural Description from Lesson 1

#### **Truth Table**

abc|f

-----|--

000|0

001|0

010|0

011|1

100 | 0

101|1

110|1

111|1

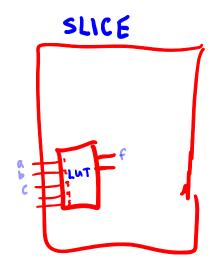

## **Structural Description**

- Entity declaration

- i/o ports ("outline" of the circuit)

- Architecture body

- Signal declaration wirts

- Each concurrent statement

- Can be thought as a circuit part

- Contains timing information

- Arch body can be thought as a "collection of parts"

- What's the difference between this and a C program?

## **Structural Description**

- In structural view, a circuit is constructed by smaller parts.

- Structural description specifies the types of parts and connections.

- Essentially a textual description of a schematic

- Done by using "component" in VHDL

- First declared (make known)

- Then instantiated (used)

## Structural Description – Component Declaration

```

-- These lines are similar to a #include in C

library IEEE;

use IEEE.std logic 1164.all;

library unisim;

-- Use these libraries if you are using primitive components

use unisim.vcomponents.all;

entity majority is

a, b, c:

in std_logic;

port(

out std_logic);

end majority;

architecture structure of majority is

component AND2

port (i0, i1 : in std_logic;

: out std logic);

end component;

component OR3

port (i0, i1, i2

: in std_logic;

: out std_logic);

0

end component;

s1, s2, s3: std_logic;

-- wires which begin and end in the component

signal

```

## Structural Description – Component Instantiation

begin

3 instantiat

Shorthand notation?

unit1: AND2  $-- s1 \le a \text{ and } b$ ; port map (  $i0 \Rightarrow a$ i1 => b, o => s1);AND2 unit2: port map (  $-s2 \le b$  and c; i0 => b,  $i1 \Rightarrow c$ , o => s2);AND2 unit3:  $-- s3 \le a \text{ and } c;$ port map (  $i0 \Rightarrow a$  $i1 \Rightarrow c$ , o => s3);unit4: OR3  $-- f \le s1 \text{ or } s2 \text{ or } s3;$ port map ( i0 => s1, i1 => s2,

> i2 => s3,o => f);

wait 4

end structure;

### Lesson 1 example code

#### Is this Behavioral or Structural code?

```

entity majority is

port( a, b, c: in std logic;

f:

out std logic);

end majority;

architecture structure of majority is

signal s1, s2, s3: std logic; -- wires which begin and end in the component

begin

s1 <= a and b; -- These statements are called

s2 <= b and c; -- concurrent signal assignments.

s3 <= a and c; -- They all happen at the same time

f <= s1 or s2 or s3; -- unlike a regular programming lang.

end structure;

```

#### **Behavioral**

**Good Example for HW2?**

A behavioral description of a component describes what the circuit does rather than how it is done.

```

library IEEE;

-- These lines are similar to a #include in C

use IEEE.std_logic_1164.all;

entity majority is

in std_logic;

a, b, c:

port(

out std logic);

end majority;

architecture Behavioral of majority is

begin

f \le =

'0' when a='0' and b='0' and c='0' else

'0' when a=0' and b=0' and c=1' else

'0' when a='0' and b='1' and c='0' else

'1' when a='0' and b='1' and c='1' else

'0' when a='1' and b='0' and c='0' else

'1' when a='1' and b='0' and c='1' else

'1' when a='1' and b='1' and c='0' else

'1':

-- essentially an enumeration of a truth table

end Behavioral;

```

### **Behavioral**

**Good Example for HW2?**

#### Concatenation operator helps make code more readable

```

-- These lines are similar to a #include in C

library IEEE;

use IEEE.std_logic_1164.all;

entity majority is

in std_logic;

a, b, c:

port(

out std_logic);

end majority;

architecture Behavioral of majority2 is

signal temp: std_logic_vector(2 downto 0);

begin

temp <= a & b & c;

f \le =

'0' when temp = "000" else

'0' when temp = "001" else

'0' when temp = "010" else

'1' when temp = "011" else

'0' when temp = "100" else

'1' when temp = "101" else

'1' when temp = "110" else

'1';

end Behavioral;

```

Concatenation Operator

Double quotes for std\_logic\_vectors

Did we need k-map simplification?

## **Combinational vs Sequential**

■ What is the difference between combinational and sequential? ←

#### Literals

#### In VHDL they are called literals (not a constant)

hexDigit: std\_logic\_vector (3 downto 0);

...hexDigit = x"D" else

...hexDigit = "0101" else

HW#2?

C cole? | VHDL. hexDigit = d"12" else

"=" - used to compare

"<=" - used to assign

## **Testbenches**

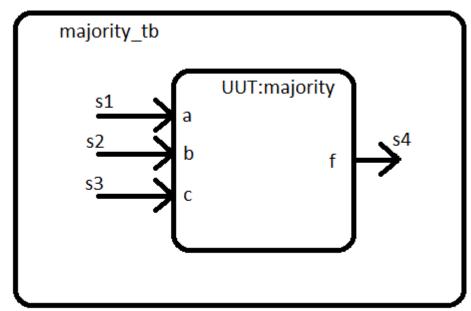

## Testbench – Component **Declaration and Instantiation**

```

2 unt: majority PORT MAP ($1,52,53,54).

ENTITY majority_tb IS

← Nothing in here?

END majority_tb;

ARCHITECTURE behavior OF majority_tb IS

COMPONENT majority

PORT(

a: IN std_logic;

majority tb

```

```

b: IN std_logic;

c: IN std_logic;

f:OUT std_logic);

END COMPONENT:

```

signal s1, s2, s3, s4: std\_logic;

begin

uut: majority PORT MAP (

$a \Longrightarrow s1$ ,

b => s2,

$c \Rightarrow s3$ ,

f => s4);

end

## Testbench – Component Declaration and Instantiation

#### ■ Test Vector Setup:

```

1. CONSTANT TEST_ELEMENTS:integer:=8;

2. SUBTYPE INPUT is std_logic_vector(2 downto 0);

3. TYPE TEST_INPUT_VECTOR is array (1 to TEST_ELEMENTS) of INPUT;

4. SIGNAL TEST_INPUT: TEST_INPUT_VECTOR := ("000", "001", "010", "011", "100", "101", "111");

**SEE TEST_ONTPUT**

```

## Loop to apply the 8 test input vectors to majority circuit

```

for i in 1 to TEST_ELEMENTS loop

testVector <= test_input(i);</li>

wait for 1 us;

assert f = test_output(i)

report "Error in majority circuit for input " & integer'image(i)

severity failure;  warning?

end loop;

```

## **Simulation Experimentation**

- How to add and remove waveforms to the waveform view.

- How to change the radix of a vector waveform

- How to change the colors of the waveforms.

- How to transcend the design hierarchy.

- How to observe signal values in design hierarchy.

- How to observe signals values in the VHDL code.

- How to save a load a simulation waveform wcfg file.

- Scan codes?

- Code, testbench, simulation plot (snip)

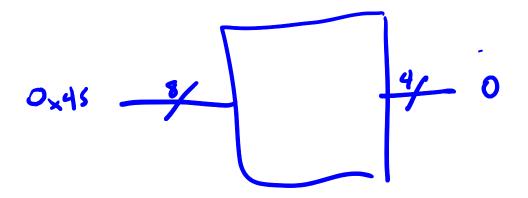

2. In the following problem, you will build vhdl function called Scancode decoder which processes keyboard scancodes. When you press a key on a keyboard, the keyboard sends an 8-bit code to the computer called a PS2 scancode. Each key has its own scancode listed below. The relationship between the keys and their scancode is not based on ASCII nor any other discernible pattern.

| Keyboard Key | Scancode (in hex) |

|--------------|-------------------|

| 0            | 0x45              |

| 1            | 0x16              |

| 2            | 0x1E              |

| 3            | 0x26              |

| 4            | 0x25              |

| 5            | 0x2E              |

| 6            | 0x36              |

| 7            | 0x3D              |

| 8            | 0x3E              |

| 9            | 0x46              |

Build a function which converts an 8-bit scancode for the digits 0-9 into a 4-bit hexadecimal values.

| Nomenclature: | Scancode decoder                                                                                                                                                                                                                                                     |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Input:   | D = std_logic_vector(7 downto 0);                                                                                                                                                                                                                                    |

| Data Output:  | H = std_logic_vector(3 downto );                                                                                                                                                                                                                                     |

| Control:      | none                                                                                                                                                                                                                                                                 |

| Status:       | none                                                                                                                                                                                                                                                                 |

| Behavior:     | Converts the scancode d, representing a the key of a decimal digit, into its 4-bit value. For example, if D = 25_16, the scancode for the character "4", then the converter should output H = 0100_2. Assume that the inputs are always legal hexadecimal scancodes. |

Use the when statement syntax to describe the output in terms of the input.

see slide